CXL을 공부하기 위해 스펙문서부터 읽어보자.

CXL은 가속기를 지원하도록 설계된 동적 다중 프로토콜 기술입니다.

메모리 장치. CXL은 유사한 I/O 의미 체계를 포함하는 풍부한 프로토콜 세트를 제공합니다.

PCIe(예: CXL.io), 캐싱 프로토콜 의미(예: CXL.cache) 및 메모리 액세스

개별 또는 패키지 내 링크에 대한 의미 체계(예: CXL.mem). CXL.io가 필요합니다

검색 및 열거, 오류 보고, CXL 메모리 및 호스트에 대한 P2P 액세스

물리적 주소(HPA) 조회. CXL.cache 및 CXL.mem 프로토콜은 선택적으로 포함될 수 있습니다.

특정 가속기 또는 메모리 장치 사용 모델에 의해 구현됩니다. 안

CXL의 중요한 이점은 대기 시간이 짧고 대역폭이 높은 경로를 제공한다는 것입니다.

가속기는 시스템에 액세스하고 시스템은 연결된 메모리에 액세스합니다.

CXL 장치. 아래 그림 1-1은 에 부착된 장치를 보여주는 개념도이다.

CXL을 통한 호스트 프로세서.

CXL 2.0 사양은 CXL 1.1 사양 이상의 추가 사용 모델을 지원하는 동시에 CXL 1.1(및 CXL 1.0) 사양과 완전히 역호환됩니다. 관리형 핫 플러그, 보안 강화, 영구 메모리 지원, 메모리 오류 보고 및 원격 측정이 가능합니다. CXL 2.0 사양은 또한 팬아웃을 위한 단일 수준 스위칭 지원은 물론 메모리 장치의 다중 도메인 지원을 포함하여 여러 가상 계층에 걸쳐 장치를 풀링하는 기능도 지원합니다. 아래 그림 1-2는 각각 고유한 색상으로 표시되는 여러 가상 계층에 걸쳐 팬아웃 외에도 단일 수준 전환을 통한 메모리 및 가속기 분리를 보여줍니다. 또한 CXL 2.0 사양을 사용하면 이러한 리소스(메모리 또는 가속기)를 한 도메인에서 오프라인으로 전환하고 다른 도메인에서 온라인으로 전환할 수 있으므로 리소스 수요에 따라 리소스를 다양한 가상 계층에 걸쳐 시간 다중화할 수 있습니다.

CXL 3.0 사양은 대역폭을 두 배로 늘리는 동시에 CXL 2.0 사양 이상의 추가 사용 모델을 지원합니다. CXL 3.0 사양은 CXL 2.0 사양(및 CXL 1.1 및 CXL 1.0 사양)과 완전히 역호환됩니다. 최대 데이터 전송률은 PAM-4 신호를 통해 64.0GT/s로 두 배 증가하며, CRC 및 FEC와 함께 PCIe 기본 사양 PHY를 활용하여 대역폭을 두 배로 늘리고 낮은 대기 시간을 위한 선택적 Flit 배열을 제공합니다. CXL 3.0 사양에서는 다중 레벨 스위칭이 활성화되어 최대 4K 포트를 지원하여 그림 1-1을 활성화합니다. CXL을 통해 프로세서에 연결된 장치의 개념도 평가 사본 소개 2022년 8월 1일 Compute Express Link 사양 개정 3.0, 버전 1.0 50 CXL은 비트리 토폴로지를 포함하여 랙 및 포드 수준으로 확장되는 패브릭으로 발전합니다. CXL 3.0 사양을 사용하면 그림 1-3에 표시된 것처럼 장치가 UIO(이전에 존재했던 MMIO 메모리 외에)를 사용하여 HDM 메모리에 직접 P2P 액세스를 수행하여 규모에 맞는 성능을 제공할 수 있습니다. 유형 2 및 유형 3 장치에서 스누프 필터 지원을 구현하여 CXL.mem에 도입된 역무효화 채널을 사용하여 직접 P2P 액세스를 활성화할 수 있습니다. 그림 1-4에 표시된 것처럼 여러 가상 계층 간의 공동 처리를 위해 여러 가상 계층에 걸친 공유 메모리 지원이 제공됩니다. CXL 프로토콜은 PCIe CEM 폼 팩터(4.0 이상), EDSFF SSF-TA-1009(개정 2.0 이상)와 관련된 모든 폼 팩터 및 PCIe를 지원하는 기타 폼 팩터와 호환됩니다.

Flex Bus

Flex Bus 포트를 사용하면 설계에서 고대역폭, 오프 패키지 링크를 통해 기본 PCIe 프로토콜 또는 CXL 제공 중에서 선택할 수 있습니다. 선택은 대체 프로토콜 협상을 통한 링크 훈련 중에 이루어지며 슬롯에 연결된 장치에 따라 달라집니다. Flex Bus는 PCIe 전기 장치를 사용하므로 PCIe 리타이머 및 PCIe를 지원하는 폼 팩터와 호환됩니다. 그림 1-5는 Flex Bus 포트 구현의 상위 레벨 다이어그램을 제공하며, 슬롯 구현과 장치가 마더보드에 납땜되어 있는 사용자 정의 구현을 모두 보여줍니다. 슬롯 구현은 Flex 중 하나를 수용할 수 있습니다. Bus.CXL 카드 또는 PCIe 카드. 하나 또는 두 개의 선택적 리타이머를 CPU와 장치 사이에 삽입하여 채널 길이를 연장할 수 있습니다. 그림 1-6에 표시된 대로 이 유연한 포트는 코히어런트 가속기 또는 스마트 I/O를 호스트 프로세서에 연결하는 데 사용할 수 있습니다. 그림 1-7은 Flex Bus.CXL 포트를 메모리 확장 포트로 사용하는 방법을 보여줍니다.

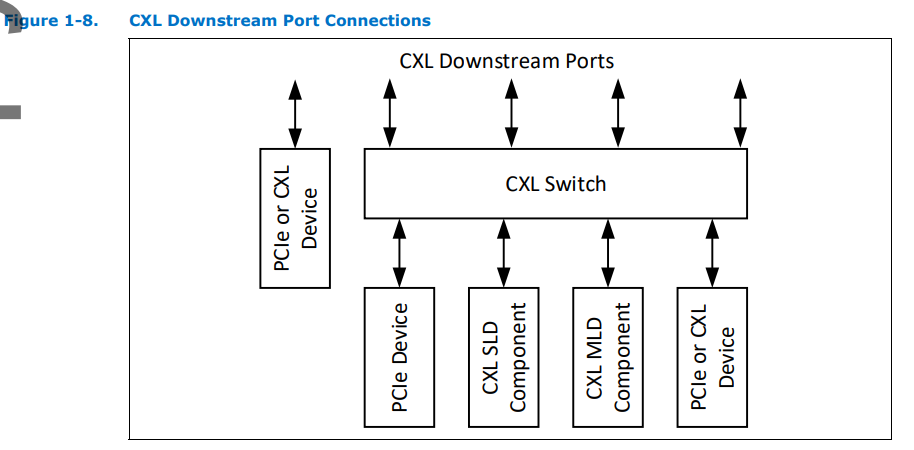

CXL 다운스트림 포트 아래에서 지원되는 연결을 보여줍니다.

Flex Bus Link 기능

Flex Bus는 기본 PCIe 프로토콜 또는 동적 다중 프로토콜 CXL을 전송할 수 있는 지점 간 상호 연결을 제공하여 PCIe 전기 장치를 통해 I/O, 캐싱 및 메모리 프로토콜을 제공합니다. 기본 링크 속성에는 다음 기능에 대한 지원이 포함됩니다.

• 기본 PCIe 모드, PCIe 기본 사양에 정의된 전체 기능 지원

• 이 사양에 정의된 CXL 모드

• PCIe 및 CXL 프로토콜 모드 구성

• PAM4의 경우 신호 속도는 64GT/s이고 저하된 속도는 CXL 모드에서 32GT/s, 16GT/s 또는 8GT/s입니다. 그렇지 않은 경우 신호 속도는 32GT/s, 저하된 속도는 CXL 모드에서 16GT/s 또는 8GT/s입니다.

• CXL 모드에서 x16, x8, x4, x2(저하 모드) 및 x1(저하 모드)에 대한 링크 너비 지원 • CXL 모드에서 x4에 대한 분기(Link Subdivision이라고도 함) 지원

Flex 버스 계층화 개요

Flex Bus 아키텍처는 그림 1-9에 표시된 것처럼 여러 계층으로 구성됩니다. CXL 트랜잭션(프로토콜) 계층은 CXL.io를 처리하는 로직과 CXL.cache 및 CXL.mem을 처리하는 로직으로 세분화됩니다. CXL 링크 레이어도 같은 방식으로 세분화됩니다. CXL.cache 및 CXL.mem 로직은 트랜잭션 레이어와 링크 레이어 내부. CXL 링크 레이어는 두 로직 스트림의 트래픽을 인터리브하는 CXL ARB/MUX와 인터페이스합니다. 또한 PCIe 트랜잭션 및 데이터 링크 계층은 선택적으로 구현되며, 구현된 경우 각각 CXL.io 트랜잭션 및 링크 계층과 수렴할 수 있습니다. 링크 훈련 프로세스의 결과로 트랜잭션 및 링크 계층은 PCIe 모드 또는 CXL 모드에서 작동하도록 구성됩니다. 호스트 CPU는 아마도 두 모드를 모두 구현하는 경우 가속기 AIC는 CXL 모드만 구현하도록 허용됩니다. Flex Bus 물리적 계층의 논리적 하위 블록은 링크 트레이닝 중 대체 모드 협상 결과에 따라 PCIe 모드 또는 CXL 모드에서 작동할 수 있는 통합 논리적 물리적 계층입니다.

'cxl' 카테고리의 다른 글

| CXL architecture (0) | 2023.09.01 |

|---|---|

| cxl kconfig (0) | 2023.08.30 |

댓글